(1) 情報技術の心臓部を担うLSI

LSI(Large Scale Integration)は、現在ではナノメータ(10 億分の1メートル)レベルの微細加工技術によって、何と数十億個の電子素子(トランジスタ)がたった1cm四方ほどの小さなチップの中に集積され、様々な機能を実現しています。パソコンや携帯電話をはじめとして、デジタルテレビ、ゲーム機、自動車などの先端電子機器は全てLSIによって実現されており、人類に多大な恩恵を与えています。まさに、LSIは情報技術の心臓部であるということができ、またLSIがなければ、情報技術そのものが成り立ちません。

(2) ムーアの法則

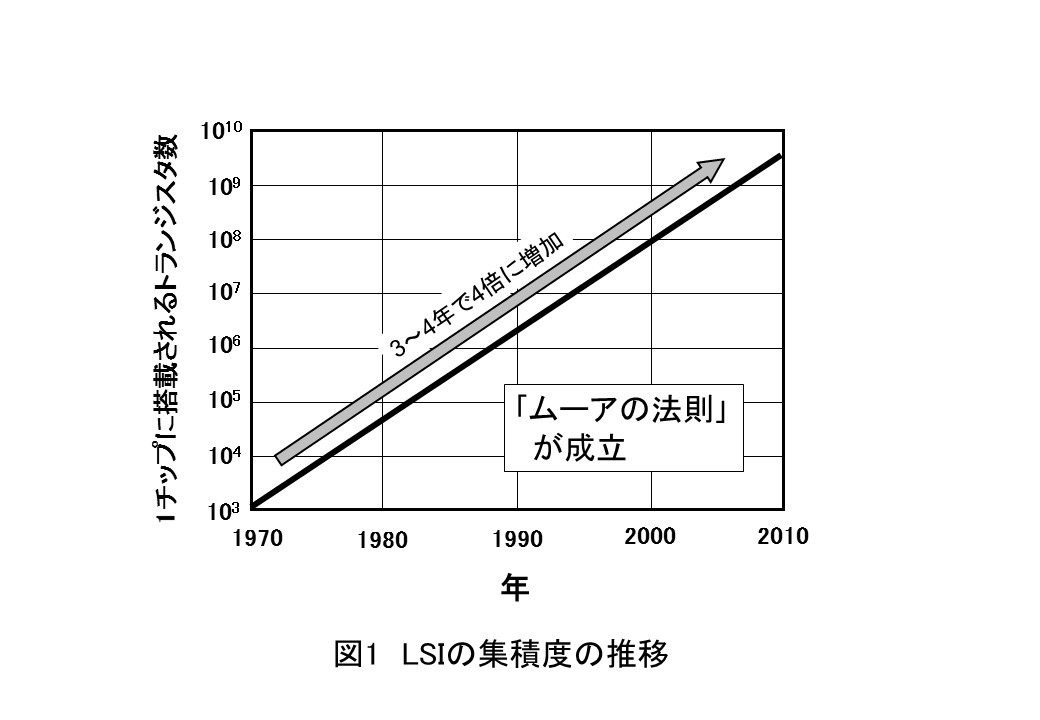

1965年に、インテル社の創始者の一人であるゴードン・ムーアという人が「1チップのトランジスタ数は3~4年ごとに4倍になる」と予言しました。これは、微細加工技術の進歩によってLSIの集積密度が指数関数的に増加していくとうい予言であり、それに伴ってLSIの機能や性能もまた指数関数的に向上していくことを意味しています。図1に過去40年間における1チップ上に搭載されるトランジスタ数のおおよその推移を示します。微細加工技術は、1970頃は10ミクロン程度であったものが、現在(2016年)では何と22ナノメートルまで進んでおり、これによって1チップに搭載されるトランジスタは、およそ3.6年ごとに4倍のペースで増加しています。このように、ムーアの法則は過去40年以上にわたって全く変わることなく実現されており、これが情報技術の進歩そのものといっても過言ではありません。そして、これからも継続的に人類に恩恵を与え続けることが期待されています。

(3) LSI設計はまさに情報技術

LSIの大規模化によって利用者は多大な恩恵を享受ことができますが、LSIの設計者にとってはどんどん設計が大変になっています。上でも述べたように現在の高機能LSIでは、1チップに10億個以上のトランジスタが搭載されますので、10億個以上のトランジスタを適切に並べて、これらを10億本以上の微細な配線でつなぐ必要があります。これは、人間の手作業では一生かかっても完成させることは不可能です。したがって、現在のLSI設計はほとんどがコンピュータによる自動設計となっています。もちろん、全体の構成や機能は人間が頭で考えて大まかな設計を手作業で行いますが、その後の詳細な設計は様々な設計ツール(ソフトウエア)を用いて自動で行われます。大規模なLSIの設計では、極めて大量の情報処理が必要となり、これを実現するためにトランジスタを配置・配線するためのツール、動作を確認するためのシミュレータなどがどんどん開発および改良され、またコンピュータの性能もその世代の最高のものが要求されます。つまり、その時代の最高のハードウエア技術とソフトウエア技術を総動員して何とか設計が可能となっているのが現状です。言い換えれば、情報技術の心臓部として働くLSIもまた、最新の情報技術によって作られているということができ、この状況は今後も続くと考えられます。

(4) ばらつきとの戦い

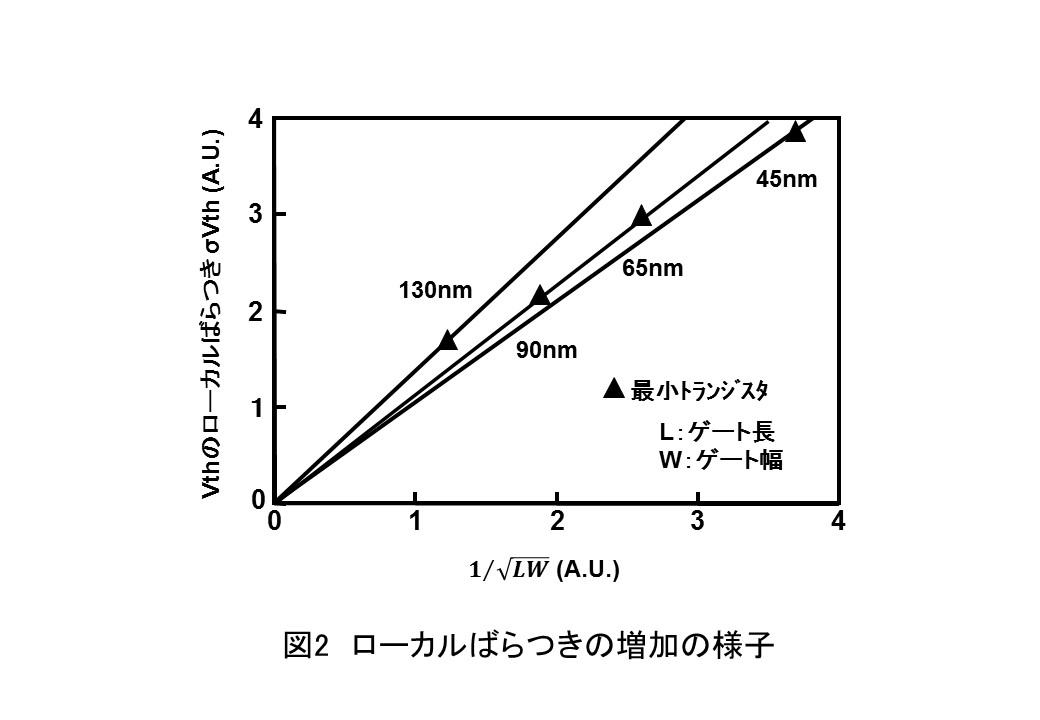

LSIの製造技術は、どんどん微細化が進んでいますが、微細化に伴い、トランジスタ特性のばらつきが顕著になっています。トランジスタ特性のばらつきには、チップの中で全トランジスタの特性が一斉に同方向に変動する「グローバルばらつき」と、チップの中でトランジスタ毎にランダムに変動する「ローカルばらつき」があります。微細化のレベルが90nm世代までは、グローバルなばらつきが主な要因でしたが、65nm世代以降では、ローカルなばらつきが増大して顕著になっています。図2に、130nm~65nmの各世代におけるトランジスタのしきい値電圧Vth(トランジスタがON/OFFする電圧のことで、トランジスタ特性の指標となる値)のローカルばらつきの増加の様子を示します。ローカルばらつきは、トランジスタのゲート面積(=ゲート長×ゲート幅)の平方根に反比例する性質を持つため、微細化による面積の減少によって急速に増大し、65nm世代以降では支配的なばらつき要因となっています。

トランジスタ特性のばらつきは、回路の動作スピードに影響を与えるため、同じように作ったチップでも、ばらつきによってスピードの速いチップと遅いチップができてしまいます。グローバルなばらつきが増大すると速いチップと遅いチップのスピードの差が大きくなり、またローカルなばらつきが増大すると一つのチップ内で速い部分と遅い部分できてしまい結局チップ全体としては遅いチップになってしまいます。LSIは、ユーザから要求された動作スピード(動作周波数)を達成したチップしか使ってもらえないので、それを達成できない遅いチップは不良品となってしまいます。つまり、ばらつきの増大によって遅いチップが増えると、動作歩留まり(作ったチップの中で正しく動くチップの割合)が低下して、製造コストが大幅に増えてしまいます。このような状況から、現在LSIを作る上で、トランジスタ特性のばらつきによる動作歩留まりの低下をどうやって改善するか、が大きな課題となっています。

(5) ばらつきに強くする技術の研究

このような、ばらつきによるLSIの動作歩留まり低下の問題を改善するために、ナノ集積システム研究室では、チップ毎の仕上がり状況に応じた自律的な電圧の最適化によって動作歩留まりを向上させる研究を行っています。本研究は、まず以下の2つの方針に基づいています。

・遅いチップは電源電圧を上昇することで速くすることができるの

で、遅く仕上がったチップを見つけて与える電圧を上げることで

動作歩 留まりの改善を図る。ただし、必要以上に電圧を上げる

と消費電力も大 きくなってしまうので、電圧の上昇は必要最小

限に留める。

・できたチップに対して、一つ一つスピードを測っていては時間が

かかるので、スピードの測定装置をチップ上に設けて、チップ内

で自動的に測定可能とする。さらに、測定されたスピードから最

適な電圧を決定して与える機構もチップ上に載せ、スピードの測

定から最適電圧の供給までのすべてをチップ上で自律的に行える

ようにする。

本研究のコンセプトを図3に示します。この図は、上で述べた方針に基づいて私たちが提案するLSIの全体構成を模式的に表したものです。通常すべてのLSIにはメモリ回路とロジック回路が搭載されるのでそれぞれのブロックを示しています。図の左側の点線で囲った部分が提案する機構で、以下の①~④の手順でスピードの検知から電圧の最適化までを行います。

①スピードの測定はリングオシレータという非常に簡単な発振器で行

う。この発振器の発振周波数を小さなカウンタ回路で測定する。

②得られた発振周波数から、Vthなどの値を算出する。この計算を行

うために小規模な演算装置(プロセッサ回路)を設ける。

③算出されたVthなどの値から最適電圧を決定する。そのために事前

にVthなどの値と最適電圧を対応付けるテーブルを作成し、これを

チップ内に持たせておく。

④決定された最適電圧に応じて電源電圧の制御を行い、所定の電圧を

メモリ回路とロジック回路に与える。

以上の機構により、チップ毎に仕上がり状態を検知してそれに応じた最適電圧を自律的に与えることができます。また、全てが簡単なデジタル処理で行われるため、チップ上の小さな回路で実現することができます。

現在、②の算出アルゴリズムや③のテーブルを開発する研究を進めており、適宜学会発表も行っています。この研究を進めることで、近い将来、チップが自律的に自身の仕上がり状況を検知して、電圧を最適化することが可能となり、その結果従来では動作不良となっていたLSIを動作可能とすることができます。本研究が、ばらつきの問題に対する有力な解決策であると考え、研究を進めています。